LEON2/3 Integer Unit - SystemC

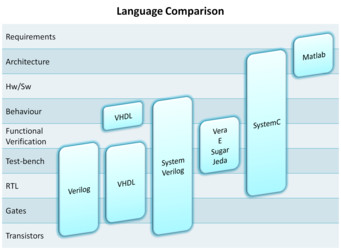

This page describes the SystemC IP-Cores relative to the Integer Unit of the LEON2 and LEON3 processors; note that, often, such high level models of hardware processors are also called Instruction Set Simulators (ISS). With respect to RTL or Gate-Level descriptions, ISSs eliminate much of the modeling and simulation overhead by focusing on the architecture status that is visible to programmers according to the Instruction-Set-Architecture (ISA); other architectural features are only modeled when strictly necessary.

Manually hand-codying such simulators is a tedious, lengthy, and error-prone task; hence the need for Architecture Description Languages (ADLs), devised to enable automatic generation of tools to support the design process starting from high-level abstract descriptions.

The design and implementation of the SystemC IP-Cores of the LEON2 and LEON3 processors presented in this page has been carried out using the TRAP Architectural Description Language.

TRAP

TRAP (TRansactional Automatic Processor generator) is a tool for the automatic generation of processor simulators starting from high level descriptions of the architecture.

TRAP is an Open Source tool released under the LGPL license; development status and periodical snapshots can be found on http://trap-gen.googlecode.com. TRAP has been developed at Politecnico di Milano with partial support from the European Space Agency.

The Instruction Set Simulators generated by TRAP are based on the OSCI SystemC 2.2.0 library and, for modeling the processor's communication interfaces, on the new OSCI TLM 2.0 standard. Depending on the desired accuracy/simulation speed trade-off, different flavors of simulators can be created.

In addition to the ISS itself, TRAP provides tools for the ISS's monitoring, debugging, exacting performance figures, etc.. Being such tools part of TRAP, they are also included in the LEON2/3 ISSs.

LEON2/3 SystemC IP-Cores

Only the integer unit of the LEON2/3 Systems-on-Chip (SoCs) is modeled: the idea is that the other elements of the SoCs, such as the cache, the AMBA buses, etc. are developed as separate SystemC IP-Cores.

Different simulators are provided, each one with different timing accuracy:

- Functional (or Standalone) without the use of SystemC: this model cannot be plugged in a system-level simulation platform, and it can just be used for the emulation of the described processor, with the aim of validating and debugging software. No performance results can be extracted from such a model, apart from statistics concerning the number of executed instructions.

- Instruction Accurate with Loosely Timed (LT) or Approximate Timed (AT) TLM 2.0 interfaces; such models exhibit high simulation speed and good timing accuracy, aroung 99.3% with respect to actual processor.

- Cycle Accurate with AT interfaces, enabling accurate timing with respect to both the communication with external memories and the processor structure (pipeline stages, hazards, bypasses, etc.). Such a model is more than one order of magnitude slower than the Instruction Accurate ones.

Simulator performance has been measured on a set of 26 applications and benchmarks taken from the MiBench suite, from standard kernels such as fft, aes, des, and complete applications like jpeg; each of these applications has been compiled using different optimization levels, yielding a total of 104 different executable files.

Assessment of the timing accuracy of the LEON2 and LEON3 Instruction Accurate models has been measured using the GRSIM simulator (from Aeroflex Gaisler) as a reference model; the same 104 executable files used to quantify the simulator speed have been executed on both GRSIM and the LEON2/3 ISSs, yielding an average accuracy of 99.3%.

For more informations on the models and please see the documents posted on the right menu of this webpage.

Licensing

The LEON2/3 SystemC IP-Cores can be licensed for space research and/or commercial use, under specific conditions to companies based in ESA member and participant states; please refer to the Related Articles posted on the right of this webpage for more information.

Developers and contributors

Luca Fossati (Politecnico di Milano / ESA) - v0.31, TRAP version 0.59 (2009 - 2012)

Germany

Germany

Austria

Austria

Belgium

Belgium

Denmark

Denmark

Spain

Spain

Estonia

Estonia

Finland

Finland

France

France

Greece

Greece

Hungary

Hungary

Ireland

Ireland

Italy

Italy

Luxembourg

Luxembourg

Norway

Norway

The Netherlands

The Netherlands

Poland

Poland

Portugal

Portugal

Czechia

Czechia

Romania

Romania

United Kingdom

United Kingdom

Slovenia

Slovenia

Sweden

Sweden

Switzerland

Switzerland